# Assembler Language Programming

for

IBM System z<sup>TM</sup> Servers

# Mini-Slides and Lecturer Notes, Version 2.00

Chapters I to VIII

John R. Ehrman

IBM Silicon Valley Lab

Note

These pages have space below the miniature copies of the lecture slides where a lecturer can write notes for added explanations, digressions, etc.

Because the font sizes used for the full-size slides do not scale exactly to the miniature forms, some of the miniature slides might overflow the space in which the full-size slides will fit. I expect that these miniature slides will be used only to connect the full-size lecture slides to these lecturer notes, so the overflows won't be a major concern.

## Second Edition (March 2016)

IBM welcomes your comments. Please address them to

John Ehrman IBM Silicon Valley Lab 555 Bailey Avenue San Jose, CA 95141 ehrman@us.ibm.com

After June 1, 2016, please address comments to

john.ehrman@comcast.net

## © Copyright IBM Corporation 2015

US Government Users Restricted Rights – Use, duplication or disclosure restricted by GSA ADP Schedule Contract with IBM Corp.

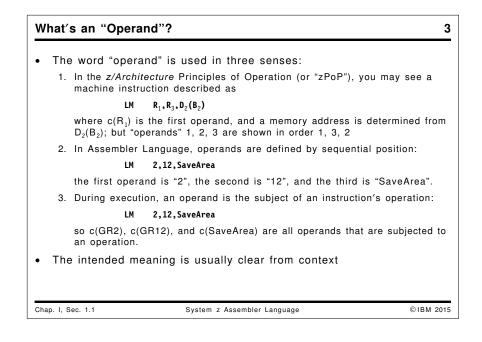

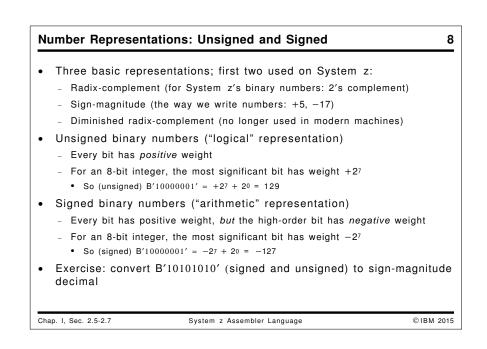

| his | chapter reviews some basic aspects of System z processors                                                                                                                                                                                                                                                           |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

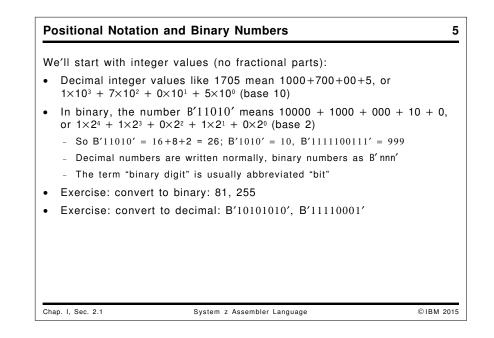

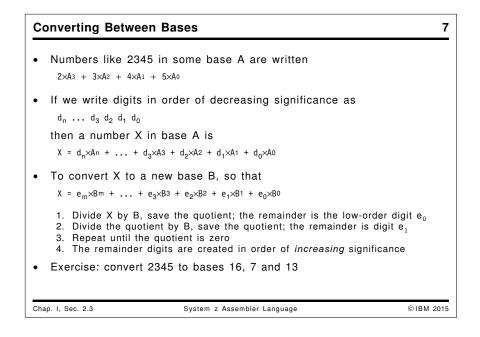

| S   | ection 1 introduces notation, terminology, and conventions<br>ection 2 describes basic properties of the number representations<br>sed in System z processors:<br>Binary and hexadecimal numbers<br>Arithmetic and logical representations<br>2's complement arithmetic<br>Conversions among number representations |

|     |                                                                                                                                                                                                                                                                                                                     |

| C  | often use a figure like this:                                                                                                                                          |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 4 4 ← Field widths                                                                                                                                                     |

|    | Field1 Field2                                                                                                                                                          |

|    | 0 34 7 🖛 Start and end positions of fields                                                                                                                             |

| ٧  | Ve number positions from <b>left</b> to <b>right</b> .                                                                                                                 |

| li | When we refer to a sequence of similar items, we may use subscripts ike $B_j$ , or appended letters like $B_j$ , or the programming-language subscript notation $B(j)$ |

| Г  | The contents of some item X is often denoted c(X)                                                                                                                      |

|    | The operators $+$ - $*$ / represent addition, subtraction, multiplication, and division, respectively                                                                  |

| 6  |                                                                                                                                                                        |

|    | o show a blank space, we sometimes use a • character                                                                                                                   |

|                |                    | the<br>f 4 b                       |                      |                           |                         |                       |                       |                        |                    |                   |                 |                 |                 | rger,           | we    | use   |

|----------------|--------------------|------------------------------------|----------------------|---------------------------|-------------------------|-----------------------|-----------------------|------------------------|--------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|-------|

| T              | he 1               | 6 po                               | ssibl                | e he                      | x va                    | lues                  | from                  | n 0 to                 | o 15               | are               | repr            | esen            | ted I           | oy 0-           | •9, A | -F    |

| 0000<br>0<br>0 | 0001<br>1<br>1     | 0010<br>2<br>2                     | 0011<br>3<br>3       | 0010<br>4<br>4            | 0101<br>5<br>5          | 0110<br>6<br>6        | 0111<br>7<br>7        | 1000<br>8<br>8         | 1001<br>9<br>9     | 1010<br>10<br>A   | 1011<br>11<br>B | 1100<br>12<br>C | 1101<br>13<br>D | 1110<br>14<br>E |       | (dec) |

| -<br>E:        | So<br>xerc<br>xerc | lecim<br>B'110<br>ise: d<br>ise: d | )10′<br>conv<br>conv | = X'1<br>ert to<br>ert to | A'; E<br>b hex<br>b dee | 3'101<br>kade<br>cima | 1′ =<br>cima<br>I: X′ | X′B′<br>I: 14<br>763′, | B′1<br>5, 5<br>X′F | 1111(<br>00<br>7' | 00111           | l' = )          | X′3E7           | ,,              |       |       |

| • E:           | xerc               | ise: (                             | conv                 | ert to                    | o bin                   | ary:                  | X′76                  | 53', )                 | 〈'F7'              |                   |                 |                 |                 |                 |       |       |

| Two's Complement                                                                                                                                            | 9         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| • Binary addition is very simple:<br>$ \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                   |           |

| • Finding the two's complement (negation) of a binary number:                                                                                               |           |

| <ul> <li>Take its ones' complement: change all 0s to 1s and 1s to 0s;<br/>then add a low-order 1 bit</li> </ul>                                             |           |

| <ul> <li>Examples, using signed 8-bit values:</li> </ul>                                                                                                    |           |

| 10000001         (signed -127)         00000001         (signed +1)           01111110         ones' complement         11111110         ones' complement   |           |

| + 1<br>01111111 (signed +127) + 1<br>11111111 (signed -1)                                                                                                   |           |

| 11111101         (signed -3)         00011111         (signed +31)           00000010         ones' complement         11100000         ones' complement    |           |

| 00000011 (signed +3) 11100001 (signed -31)                                                                                                                  |           |

| <ul> <li>Carries out of the leftmost bit: ignored for unsigned, important for sig</li> <li>But most arithmetic instructions take note of carries</li> </ul> | gned      |

| Chap. I, Sec. 2.8 System z Assembler Language                                                                                                               | ©IBM 2015 |

| Sign Extension                                                                                                   | 10     |

|------------------------------------------------------------------------------------------------------------------|--------|

| Binary numbers can be lengthened to greater precision by sign extension                                          |        |

| If the sign bit is copied to the left, the value of the number is<br>unchanged in the new, longer representation |        |

| - Examples, using signed 16-bit values extended from 8 bits:                                                     |        |

| 1111111110000001(signed -127)0000000000000001(signed +1)0000000001111111(signed +127)1111111111111111(signed -1) |        |

| - Many instructions do sign extension automatically                                                              |        |

|                                                                                                                  |        |

|                                                                                                                  |        |

| hap. I, Sec. 2.9 System z Assembler Language © IB                                                                | M 2015 |

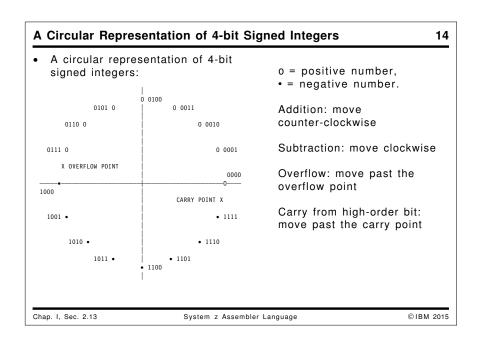

| Ac | ddition, Subtraction, and Arithmetic Overflow                                                                                                                     | 11 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| •  | All bits are added; high-order carries are lost (but noted)                                                                                                       |    |

|    | - Examples, using signed 4-bit values (range -8 $\leq$ value $\leq$ +7):                                                                                          |    |

|    | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                              |    |

|    | <ul> <li>Arithmetic addition: overflow possible only when adding like-signed operands.</li> </ul>                                                                 |    |

|    | • Actions vary: signed overflow can be ignored, or cause an "interruption"                                                                                        |    |

| •  | Unsigned (logical) addition: carries are noted, no overflows                                                                                                      |    |

|    | - Examples, using unsigned 4-bit values (range 0 $\leq$ value $\leq$ 15):                                                                                         |    |

|    | 1111 (15)       0010 (2)       1100 (12)         +0001 (1)       +0010 (2)       +1001 (9)         0000 (0, carry)       0100 (4, no carry)       0101 (5, carry) |    |

| •  | Conditional branch instructions (described in Section 15) can te<br>overflow (arithmetic addition or subtraction) and carries (logica<br>addition or subtraction) |    |

|    |                                                                                                                                                                   |    |

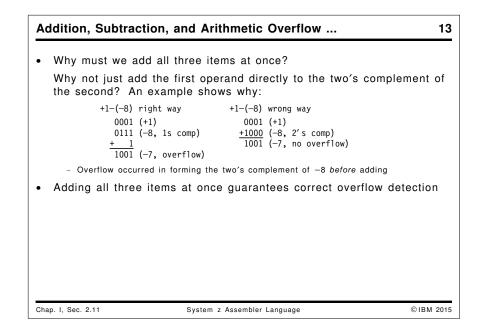

| • | Subtraction is slightly                                              | , more complicate   | ed than addition                                                        |            |

|---|----------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------|------------|

|   | <b>U</b> .                                                           | •                   | ond (subtrahend) opera                                                  | nd         |

|   |                                                                      | end) and compleme   | nted second operands a                                                  |            |

|   | - Examples, using sigr                                               | red 4-bit values:   |                                                                         |            |

|   | -1-(+1)<br>1111 (-1)<br>1110 (+1,comp)<br>+ <u>1</u> 110 (-2, carry) | 0010 (+2)           | 3-5<br>0011 (+3)<br>1010 (+5,comp)<br><u>+ 1</u><br>1110 (-2, no carry) |            |

|   | <ul> <li>Arithmetic subtractio<br/>noted</li> </ul>                  | n: overflows possib | le; logical subtraction: c                                              | arries are |

| • | Adding the first oper second operand work                            |                     | •                                                                       | of the     |

|   |                                                                      |                     |                                                                         |            |

|   |                                                                      |                     |                                                                         |            |

|                  | terns from logic<br>only the overflow |                    |                     |                     |

|------------------|---------------------------------------|--------------------|---------------------|---------------------|

| -                | esentations for                       | ,                  |                     | unterent            |

| Binary<br>Digits | Logical<br>Representation             | Sign-<br>Magnitude | Ones'<br>Complement | Two's<br>Complement |

| 0000             | 0                                     | +0                 | +0                  | 0                   |

| 0001             | 1                                     | +1                 | +1                  | +1                  |

| 0010             | 2                                     | +2                 | +2                  | +2                  |

| 0011             | 3                                     | +3                 | +3                  | +3                  |

| 0100             | 4                                     | +4                 | +4                  | +4                  |

| 0101             | 5                                     | +5                 | +5                  | +5                  |

| 0110             | 6                                     | +6                 | +6                  | +6                  |

| 0111             | 7                                     | +7                 | +7                  | +7                  |

| 1000             | 8                                     | -0                 | -7                  | -8                  |

| 1001             | 9                                     | -1                 | -6                  | -7                  |

| 1010             | 10                                    | -2                 | -5                  | -6                  |

| 1011             | 11                                    | -3                 | -4                  | -5                  |

| 1100             | 12                                    | -4                 | -3                  | -4                  |

| 1101             | 13                                    | -5                 | -2                  | -3                  |

| 1110             | 14                                    | -6                 | -1                  | -2                  |

| 1111             | 15                                    | -7                 | -0                  | -1                  |

| Exercise Answers                                   |                             | 16         |

|----------------------------------------------------|-----------------------------|------------|

| • Slide 5:                                         |                             |            |

| - B'01010001', B'111111                            | 1'                          |            |

| - 170, 241                                         |                             |            |

| • Slide 6:                                         |                             |            |

| - X'91', X'1F4'                                    |                             |            |

| - 1891, 247                                        |                             |            |

| - B'11101100011', B'1111                           | 01111'                      |            |

| • Slide 7:                                         |                             |            |

| - X'929', 6560 <sub>7</sub> , 10B5 <sub>13</sub> . |                             |            |

| • Slide 8:                                         |                             |            |

| 86, 170                                            |                             |            |

|                                                    |                             |            |

|                                                    |                             |            |

|                                                    |                             |            |

|                                                    |                             |            |

| Chap. I, Sec. 2.1-2.7                              | System z Assembler Language | © IBM 2015 |

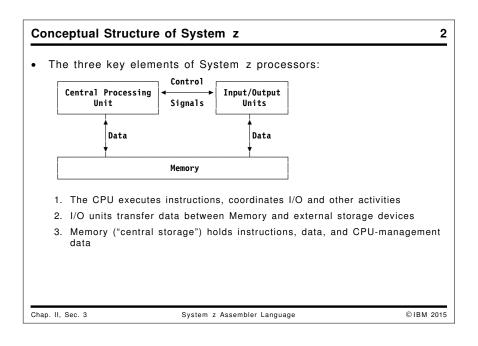

| Chapter II. System z                                                                                                                                                                                                         | 1   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| This chapter's three sections introduce the main features of System z processors:                                                                                                                                            |     |

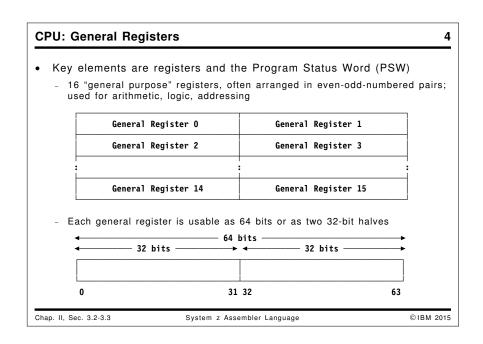

| <ul> <li>Section 3 describes key processor structures: the Central Processing<br/>Unit (CPU), memory organization and addressing, general purpose<br/>registers, the Program Status Word (PSW), and other topics.</li> </ul> | I   |

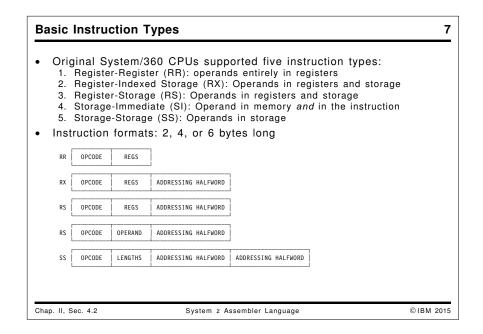

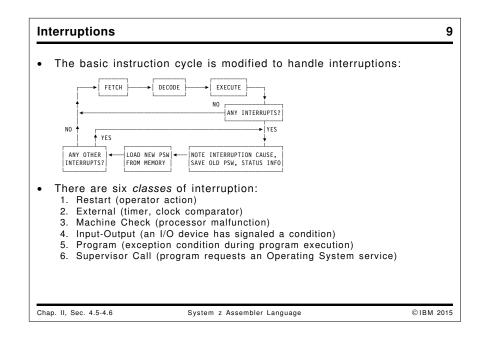

| • Section 4 discusses the instruction cycle, basic machine instruction types and lengths, exceptions and interruptions and their effects on the instruction cycle.                                                           | he  |

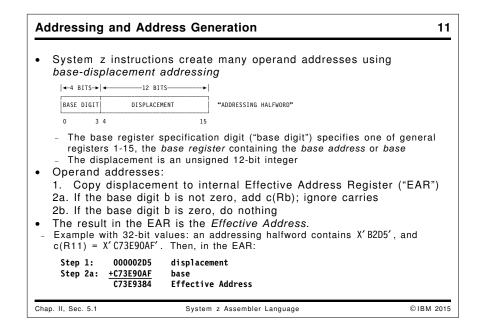

| <ul> <li>Section 5 covers address calculation, the "addressing halfword",<br/>Effective Addresses, indexing, addressing problems, and virtual<br/>memory.</li> </ul>                                                         |     |

|                                                                                                                                                                                                                              |     |

|                                                                                                                                                                                                                              |     |

| Chap. II, Sec. 3-5 System z Assembler Language © IBM 2                                                                                                                                                                       | 015 |

|     | name | •      | ps w | vith a | addro | esse | s div | /ISIDI | e by | the  | grou | ib le | ngth | hav  | e sp  | ecia |     |

|-----|------|--------|------|--------|-------|------|-------|--------|------|------|------|-------|------|------|-------|------|-----|

| 8DF | 8E0  | 8E1    | 8E2  | 8E3    | 8E4   | 8E5  | 8E6   | 8E7    | 8E8  | 8E9  | 8EA  | 8EB   | 8EC  | 8ED  | 8EE   | 8EF  | 8F0 |

|     |      |        |      |        |       |      |       |        | ļ    |      |      |       |      |      |       |      |     |

| 1   | Truc | tions  |      |        |       |      |       | gie    | byte | s, g | rou  | os a  | s sh | iowr | i, or | stri | ng  |

|     |      | of (al | mos  | n) a   | ,     |      |       |        |      |      |      |       |      |      |       |      |     |

|     |      | of (al | mos  | n) a   |       |      |       |        |      |      |      |       |      |      |       |      |     |

| -       | Used for flo |         |              | riginally 4:<br>some instructions u                    | se only the left half |

|---------|--------------|---------|--------------|--------------------------------------------------------|-----------------------|

|         |              | 64 BITS |              | ▶                                                      |                       |

| ſ       |              | F0      |              |                                                        |                       |

| ŀ       |              | F2      |              |                                                        |                       |

|         |              | F4      |              |                                                        |                       |

| ſ       |              | F6      |              | 1                                                      |                       |

| _       | 0            |         |              | 63                                                     |                       |

| Pr<br>- | Key compo    | `       | ction Length | ally a 128-bit qua<br>Code (ILC), Condit<br>dress (IA) | ,                     |

| Basic Instruction Cycle                                                                                                                                                                                                   | 6         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| • Easiest to visualize in three steps:                                                                                                                                                                                    |           |

|                                                                                                                                                                                                                           |           |

| <ol> <li>Fetch: bring instruction from memory, determine its type and lengt         <ul> <li>Add its length to PSW's Instruction Address (IA) to form address of "Next<br/>Sequential Instruction"</li> </ul> </li> </ol> |           |

| 2. Decode: determine validity of instruction; access operands                                                                                                                                                             |           |

| <ol><li>Execute: perform the operation; update registers and/or memory a required</li></ol>                                                                                                                               | S         |

| • Possible problems, interruptions (more at slides 9-10)                                                                                                                                                                  |           |

| <ul> <li>Fetch: invalid instruction address</li> </ul>                                                                                                                                                                    |           |

| <ul> <li>Decode: invalid or privileged instruction</li> </ul>                                                                                                                                                             |           |

| <ul> <li>Execution: many possibilities!</li> </ul>                                                                                                                                                                        |           |

|                                                                                                                                                                                                                           |           |

| Chap. II, Sec. 4.1 System z Assembler Language                                                                                                                                                                            | ©IBM 2015 |

| 11xxxxxx 6-byte instructions such as SS-type                                                                      |      |

|-------------------------------------------------------------------------------------------------------------------|------|

| Instruction Length Code (ILC) set to the number of halfwords in instruction (1,2,3)                               | the  |

| ILC<br>(decimal)         ILC (binary)         Instruction types         Opcode bits<br>0-1         Instruction le | ngth |

| 0 B' 00' Not availab                                                                                              | le   |

| 1 B'01' RR B'00' One halfwo                                                                                       | rd   |

| 2 B'10' RX B'01' Two halfwor                                                                                      | rds  |

| 2 B'10' RS, SI B'10' Two halfwor                                                                                  | rds  |

| 3 B'11' SS B'11' Three halfwo                                                                                     | ords |

| Inter   | ruptions                                                                                                         | 10         |

|---------|------------------------------------------------------------------------------------------------------------------|------------|

| • Th    | e CPU saves the current ("old") PSW, loads a new PSW                                                             |            |

|         | Supervisor saves status information, processes the condition                                                     |            |

|         | Supervisor can return to interrupted program by loading old PSW                                                  |            |

| • Sc    | ome "popular" Program Interruption Codes (IC):                                                                   |            |

|         | =1 Invalid Operation Code.                                                                                       |            |

|         | <ul> <li>4 Access, Protection: program has referred to an area of<br/>to which access is not allowed.</li> </ul> | memory     |

| IC      | =6 Specification Error: can be caused by many conditions.                                                        |            |

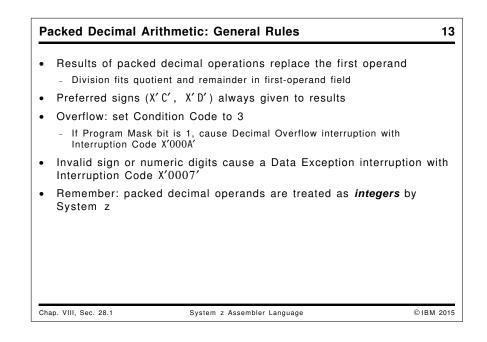

|         | =7 Data Exception: invalid packed decimal data, or by floa conditions described in Chapter IX.                   | ting-point |

| IC      | =8 Fixed-Point Overflow: fixed-point binary result too large                                                     |            |

|         | =9 Fixed-Point Divide Exception: quotient would be too big<br>divisor is zero.                                   |            |

| IC      | <b>= A</b> Decimal Overflow: packed decimal result too large.                                                    |            |

| IC      | <b>B</b> Decimal Divide: packed decimal quotient too large, or is zero.                                          | a divisor  |

| IC      | <b>=C</b> Hexadecimal floating-point exponent overflow: result to                                                | o large.   |

| IC      | <b>= D</b> Hexadecimal floating-point exponent underflow: result                                                 | too small. |

| Chen II | Sec. 4.5-4.6 System z Assembler Language                                                                         | © IBM 2015 |

| In  | dexi      | ng and V                                        | irtual            | Add              | ress              | es                                                                  |                       | 12   |

|-----|-----------|-------------------------------------------------|-------------------|------------------|-------------------|---------------------------------------------------------------------|-----------------------|------|

| •   | RX        | type instru                                     | uction            | s cor            | ntain a           | an <i>index register</i> s                                          | pecification digit x: |      |

|     |           | opcode                                          | r                 | x                | b                 | displacement                                                        |                       |      |

|     | - 1       | ndexed Effe                                     | ctive             | Addre            | ss cal            | culation adds two mo                                                | re steps:             |      |

|     |           |                                                 | •                 |                  |                   | zero, add c(Rx); ig<br>, do nothing                                 | nore carries          |      |

|     |           | Example: RX<br>c(R11) = X'                      |                   |                  |                   |                                                                     | ) = X' FEDCBA98', and |      |

|     |           | Step 1:<br>Step 2a:<br>Step 3a: <u>+</u><br>(1) | C73E90<br>FEDCBA  | AF<br>98         | index             | from R11)                                                           | carry ignored         |      |

| •   | -  <br>-  | DAT transla                                     | tes ap<br>iting S | plicat<br>Systen | ion ad<br>1 bette | Address Translatio<br>dresses into "real" a<br>er manage "actual" m | ddresses              |      |

| Cha | ap. II, S | Sec. 5.3,5.6                                    |                   |                  | System            | z Assembler Language                                                | ©IBM                  | 2015 |

|   | is chapter describes fundamental concepts of Assembler Language ogramming.                                                                                                                                                     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

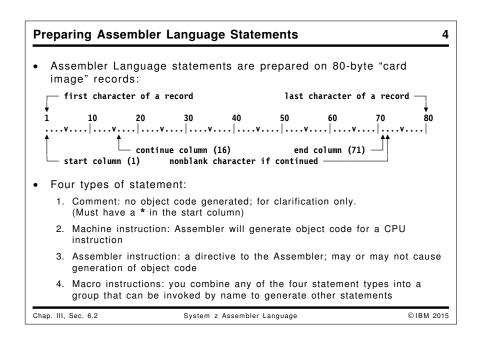

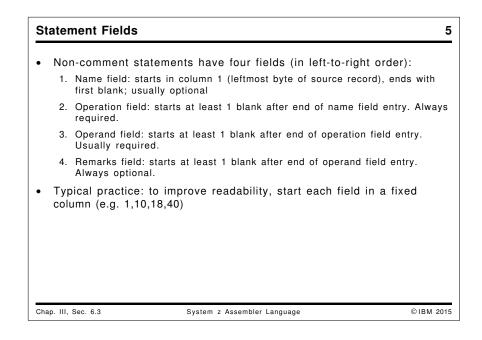

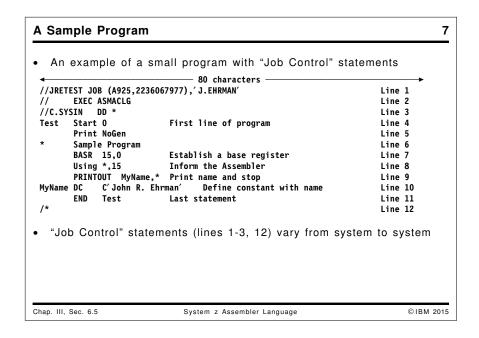

| • | Section 6 provides an overview of assembling, linking and loading for execution; conventions for preparing Assembler Language programs; and some helpful macro instructions that perform simple I/O and conversion operations. |

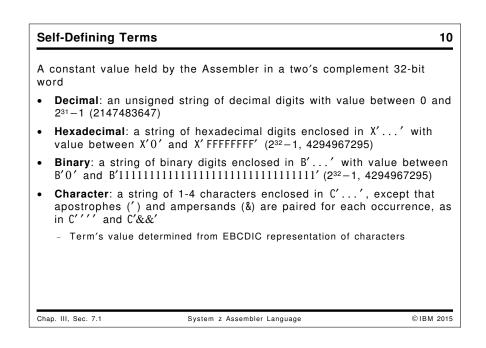

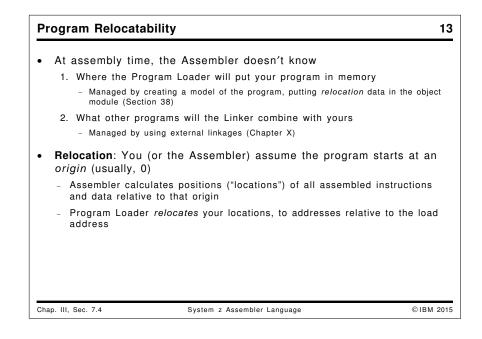

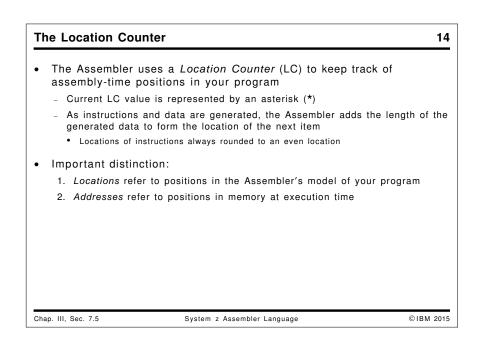

| • | Section 7 discusses key concepts relating to symbols and "variables".                                                                                                                                                          |

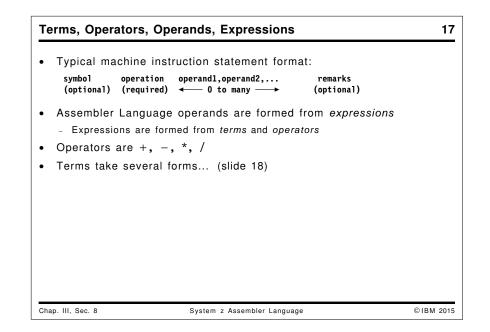

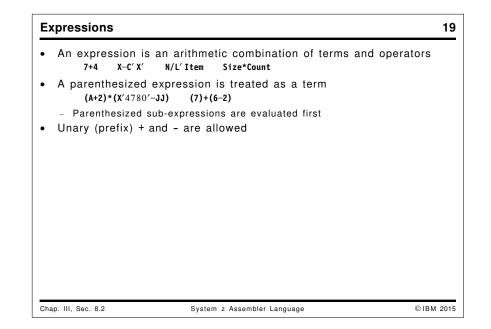

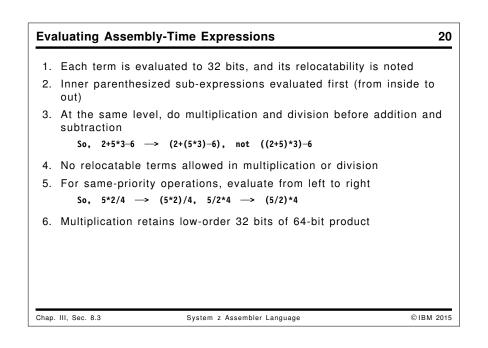

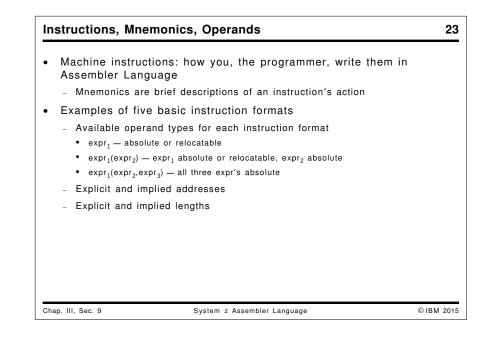

| • | Section 8 investigates the elements of expression evaluation, and the basic Assembler Language operand formats used by instructions.                                                                                           |

| • | Section 9 introduces typical instructions and how to write Assembler Language statements for them.                                                                                                                             |

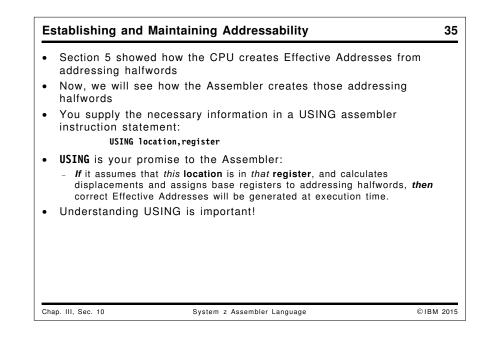

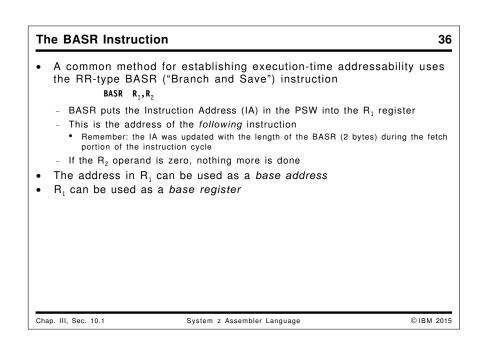

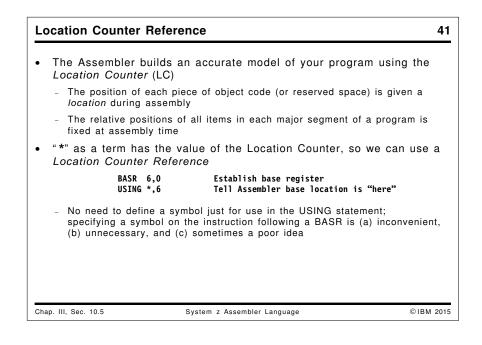

| • | Section 10 shows how the Assembler calculates displacements and assigns base register values in Addressing Halfwords, and introduces the important USING and DROP assembler instructions.                                      |

|   |                                                                                                                                                                                                                                |

| As  | ssembler Language                                                                                                                                                                                            | 2    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •   | The Assembler helps you prepare instructions for execution on System z                                                                                                                                       |      |

| •   | Gives you maximum control over selection and sequencing of specifi instructions                                                                                                                              | с    |

| •   | Assembler Language itself is much simpler than other programming languages                                                                                                                                   |      |

| •   | Main difficulties are                                                                                                                                                                                        |      |

|     | <ul> <li>Learning an appropriate set of machine instructions for your applications</li> <li>Learning all the auxiliary tools and programs needed to build and use<br/>Assembler Language programs</li> </ul> |      |

|     |                                                                                                                                                                                                              |      |

|     |                                                                                                                                                                                                              |      |

| Cha | p. III, Sec. 6 System z Assembler Language ©IBM                                                                                                                                                              | 2015 |

| •   | Generally done in three stages:                                                                                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | <b>1. Assembly;</b> The <b>Assembler</b> translates the statements of your <i>source program</i> into machine language instructions and data ("object code" in the form of an <i>object module</i> for eventual execution by the CPU. |

|     | <b>2. Linking:</b> The <b>Linker</b> combines your object module with any others required for satisfactory execution. The resulting <i>load module</i> is saved.                                                                      |

|     | <b>3. Program Loading:</b> The <b>Program Loader</b> reads your load module into memory and then gives CPU control to your instructions starting at the <i>entry point</i> .                                                          |

|     | Your program then executes your instructions: reading, writing, and generating data                                                                                                                                                   |

|     |                                                                                                                                                                                                                                       |

|     |                                                                                                                                                                                                                                       |

| Cha | p. III, Sec. 6.1 System z Assembler Language ©IBM 201                                                                                                                                                                                 |

| <ul> <li>Six macro instr</li> </ul> | uctions are used extensively throughout the | e text:     |

|-------------------------------------|---------------------------------------------|-------------|

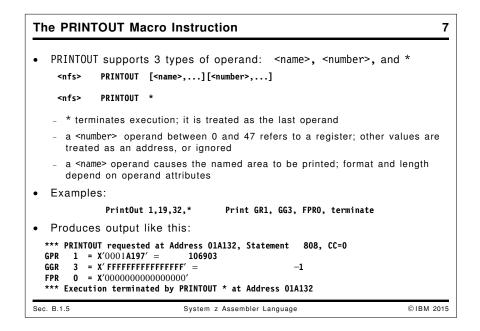

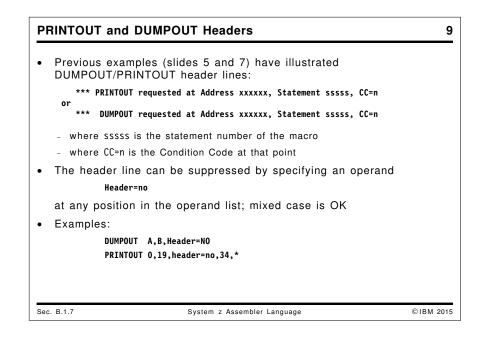

| PRINTOUT                            |                                             |             |

| Display conte                       | ents of registers and named areas of memo   | ory.        |

| READCARD<br>Read an 80-c            | character record into memory.               |             |

| PRINTLIN<br>Send a string           | g of characters to a printer.               |             |

| DUMPOUT<br>Display conte            | ents of memory in hexadecimal and charact   | er formats. |

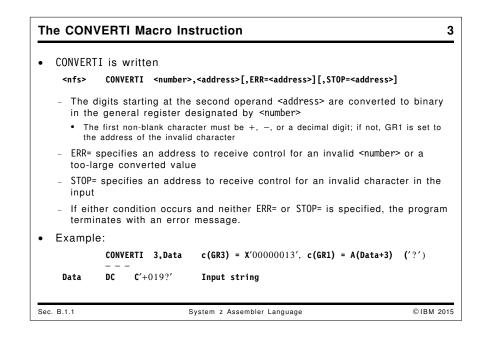

| CONVERTI<br>Convert chara           | acters to a 32- or 64-bit binary integer.   |             |

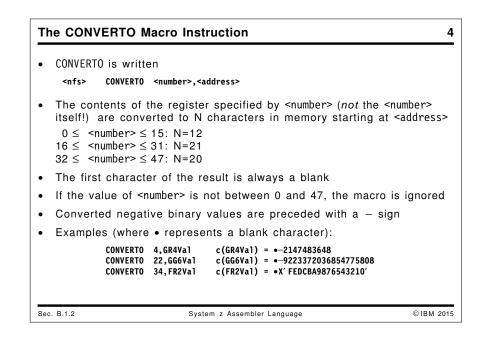

| CONVERTO<br>Convert a 32            | - or 64-bit binary integer to characters.   |             |

| Equivalent facil                    | lities may be available at your location.   |             |

# **EBCDIC Character Representation**

#### · Every character is represented by a number Char Char Hex Char Char Hex Hex Hex Blank 40 4B 81 b 82 a 83 d 84 85 f 86 с e g 87 h 88 i 89 j 91 1 93 95 k 92 94 m n 96 97 98 99 r 0 р q A2 t A3 u A4 ٧ Α5 s A6 Α7 A8 z Α9 w х у А C1 В C2 С C 3 D C4 Е C5 F C6 G C7 Н C8 Ι C 9 J D1 К D2 L D3 D5 D7 М D4 Ν 0 D6 Р D9 D8 R E2 E3 Q S Т E4 ۷ E 5 E6 E7 U W Х E9 F0 F1 Y E8 Ζ 0 1 2 F2 3 F3 4 F4 5 F5 6 F6 7 F7 8 F8 9 F9 Chap. III, Sec. 7.2 System z Assembler Language © IBM 2015

11

Notes

| Assi | gning Va                | lues to Sym          | bols                                                          | 15                        |

|------|-------------------------|----------------------|---------------------------------------------------------------|---------------------------|

| • Va | alues are               | assigned to s        | ymbols in two ways:                                           |                           |

| 1    |                         |                      | ally take the current value of the I<br>th of generated data) | ocation Counter           |

|      | MyProg1<br>Start        | Start 0<br>BASR 15,0 | Set assumed origin location O<br>Value of symbol "Start" is O |                           |

| 2    | . Sometim<br>stateme    |                      | es are assigned by the programme                              | er using an EQU           |

|      | symbol                  | EQU self-def         | fining term The most common for                               | m                         |

|      | ABS425<br>Char_A        | EQU 425<br>EQU C' A' | ABS425 has value 42<br>Char_A has value X'                    | -                         |

| 3    | . The leng<br>attribute |                      | ated data is usually assigned as th                           | ne symbol's <i>length</i> |

|      |                         |                      |                                                               |                           |

|      |                         |                      |                                                               |                           |

|      |                         |                      |                                                               |                           |

| Sy  | mbols and Variables                                                                                                                               | 16 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| •   | Symbols in high-level languages (usually called "variables") have<br>execution-time values<br>X <- 22./7. ; /* Set X to an approximation to pi */ |    |

| •   | Symbols in Assembler Language are used only at assembly time; the have <b>no</b> execution-time value (are NOT "variables")                       | у  |

|     | <ul> <li>Used as names of places in a program that may contain execution-time values</li> </ul>                                                   |    |

|     | - Symbol values simply help to organize the program                                                                                               |    |

|     |                                                                                                                                                   |    |

|     |                                                                                                                                                   |    |

|     |                                                                                                                                                   |    |

|     |                                                                                                                                                   |    |

|     |                                                                                                                                                   |    |

| Cha | ap. III, Sec. 7.7 System z Assembler Language ©IBM 2                                                                                              | 01 |

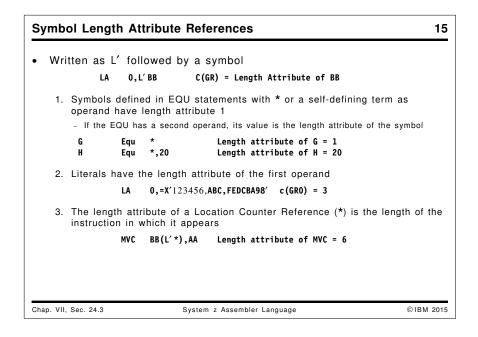

| lerms                                                      | 18        |

|------------------------------------------------------------|-----------|

| • A basic expression element is a <i>term</i>              |           |

| <ul> <li>A self-defining term (always absolute)</li> </ul> |           |

| - A symbol (absolute or relocatable)                       |           |

| - A Location Counter reference * (always relocatable)      |           |

| - A Literal (always relocatable)                           |           |

| - A symbol attribute reference (always absolute)           |           |

| • Length (L'symbol)                                        |           |

| • Integer (I'symbol)                                       |           |

| • Scale (S'symbol)                                         |           |

|                                                            |           |

|                                                            |           |

|                                                            |           |

|                                                            |           |

| Chap. III, Sec. 8.1 System z Assembler Language            | ©IBM 2015 |

| Evalua       | ting Assembly-Time Expressions                                                                                                 | 21        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|

| 7. Div       | ision discards any remainder                                                                                                   |           |

| •            | Division by zero is allowed; result is zero (!)                                                                                |           |

| 8. Ev        | aluation result is a 32-bit two's complement value                                                                             |           |

|              | locatability attribute of expression determined from relocata terms:                                                           | ıbility   |

| a.           | Pairs of terms with same attribute and opposite signs have no effe<br>"cancel"); if all are paired, the expression is absolute | ct (they  |

| b.           | One remaining unpaired term sets the attribute of the expression;<br>+ means simply relocatable, - means complexly relocatable |           |

| с.           | More than one unpaired term means the expression is complexly relocatable (a rare occurrence)                                  |           |

|              |                                                                                                                                |           |

|              |                                                                                                                                |           |

|              |                                                                                                                                |           |

|              |                                                                                                                                |           |

| Chap. III, S | Sec. 8.3 System z Assembler Language                                                                                           | ©IBM 2015 |

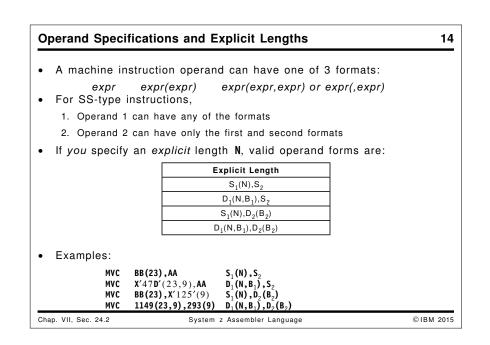

| 10 | ,                         | re "expr" = e>                         | , ,                                        |       |

|----|---------------------------|----------------------------------------|--------------------------------------------|-------|

|    | expr                      | expr <sub>1</sub> (expr <sub>2</sub> ) | $expr_1(expr_2, expr_3)$                   |       |

|    | 7<br>8*N+4<br>(91)        | A(B)                                   | 22(22,22)<br>(A)((B),(C))<br>(91)(,15)     |       |

| -  | In the sec<br>multiplicat |                                        | orms, adjacent parentheses do <i>not</i> i | imply |

| -  | In the third              | d form, expr <sub>2</sub> ca           | n be omitted if it is zero:                |       |

|    | expr                      | $r_1(,expr_3)$ [T                      | he comma is still required!]               |       |

|    |                           |                                        |                                            |       |

| Ор    | Mnem          | e some commonly used<br>Instruction | Ор                 | Mnem                 | Instruction                        |

|-------|---------------|-------------------------------------|--------------------|----------------------|------------------------------------|

| 05    | BALR          | Branch And Link                     | 06                 | BCTR                 | Branch On Count                    |

| 07    | BCR           | Branch On Condition                 | 0D                 | BASR                 | Branch And Save                    |

| 10    | LPR           | Load Positive                       | 11                 | LNR                  | Load Negative                      |

| 12    | LTR           | Load And Test                       | 13                 | LCR                  | Load Complement                    |

| 14    | NR            | AND                                 | 15                 | CLR                  | Compare Logical                    |

| 16    | OR            | OR                                  | 17                 | XR                   | Exclusive OR                       |

| 18    | LR            | Load                                | 19                 | CR                   | Compare                            |

| 1 A   | AR            | Add                                 | 1 B                | SR                   | Subtract                           |

| 1C    | MR            | Multiply                            | 1D                 | DR                   | Divide                             |

| 1E    | ALR           | Add Logical                         | 1F                 | SLR                  | Subtract Logical                   |

| ٦     | Гурісаl о     | perand field described as           | s R <sub>1</sub> , | R <sub>2</sub> — ope | rands of "expr <sub>1</sub> " form |

| Chap. | III, Sec. 9.1 | System z Asse                       | embler             | Language             | ©IE                                |

| Writing RR-Type Instructions                                                                                                        | 25     |

|-------------------------------------------------------------------------------------------------------------------------------------|--------|

| Assembler must generate machine language form of the instruction                                                                    | :      |

| OPCODE R <sub>1</sub> R <sub>2</sub>                                                                                                |        |

| <ul> <li>R<sub>1</sub> and R<sub>2</sub> designate first and second operand registers, not genera<br/>registers 1 and 2!</li> </ul> |        |

| • Since LR opcode is X'18':                                                                                                         |        |

| LR 7,3 assembles to X'1873'                                                                                                         |        |

| <ul> <li>Operands can be written as any expression with value</li> <li>0 ≤ value ≤ 15</li> </ul>                                    |        |

| LR 3*4-5,1+1+1 also assembles to X'1873'                                                                                            |        |

| - Assembly-time operands are expressions with value "7" and "3"                                                                     |        |

| - Execution-time operands are contents of general registers GR7 and GR3                                                             |        |

|                                                                                                                                     |        |

|                                                                                                                                     |        |

| Chap. III, Sec. 9.2 System z Assembler Language ©IB                                                                                 | A 2015 |

|        |                                   | e some commonly used                                                                                                                                                                         | הא-ני            | pe msu                |                      |

|--------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|----------------------|

| Dp     | Mnem                              | Instruction                                                                                                                                                                                  | Ор               | Mnem                  | Instruction          |

| 42     | STC                               | Store Character                                                                                                                                                                              | 43               | IC                    | Insert Character     |

| 44     | EX                                | Execute                                                                                                                                                                                      | 45               | BAL                   | Branch And Link      |

| 46     | вст                               | Branch On Count                                                                                                                                                                              | 47               | BC                    | Branch On Condition  |

| 4D     | BAS                               | Branch And Save                                                                                                                                                                              | 50               | ST                    | Store                |

| 54     | Ν                                 | AND                                                                                                                                                                                          | 55               | CL                    | Compare Logical      |

| 56     | 0                                 | OR                                                                                                                                                                                           | 57               | Х                     | Exclusive OR         |

| 58     | L                                 | Load                                                                                                                                                                                         | 59               | С                     | Compare              |

| δA     | А                                 | Add                                                                                                                                                                                          | 5B               | S                     | Subtract             |

| 5C     | М                                 | Multiply                                                                                                                                                                                     | 5D               | D                     | Divide               |

| δE     | AL                                | Add Logical                                                                                                                                                                                  | 5F               | SL                    | Subtract Logical     |

| S<br>( | Second o<br>"expr <sub>1</sub> (e | uction first operand field<br>operand field described a<br>xpr <sub>2</sub> )" form), as D <sub>2</sub> (X <sub>2</sub> ,B <sub>2</sub> )<br>expr <sub>1</sub> ((,expr <sub>3</sub> )" form) | s S <sub>2</sub> | ("expr <sub>1</sub> " | form), as $S_2(X_2)$ |

| w   | /riting RX-Type Instru                                                                                                                 | ctions                                                                          | 27         |

|-----|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------|

| •   | ·                                                                                                                                      | rate machine language form of the ins                                           | struction: |

| •   | First operand designa<br>Second operand usua<br>- B <sub>2</sub> , D <sub>2</sub> , and X <sub>2</sub> compor<br>address (as described | lly designates a memory reference<br>ents used at execution time to calculate m | emory      |

| •   | Since L opcode is $X'5$                                                                                                                |                                                                                 |            |

|     | 58 1 9                                                                                                                                 | · · ·                                                                           |            |

|     | L 1,200(,12                                                                                                                            | ) will generate                                                                 |            |

|     | 58 1 0                                                                                                                                 | 0C8                                                                             |            |

| Cha | ap. III, Sec. 9.4                                                                                                                      | System z Assembler Language                                                     | © IBM 2015 |

| Explicit a                 | nd Implied Addre                                                            | esses                                                           |                                         | 28 |

|----------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|----|

|                            | ys to create an ac                                                          | •                                                               | •                                       |    |

| •                          | licit: you specify the<br>ou provide the values ir                          | •                                                               | isplacement                             |    |

| - Y                        | licit: The Assembler<br>ou specify an operand o<br>ddress resolution (desci | of the form $S_2$ or $S_2(X_2)$                                 | • •                                     | -  |

| <ul> <li>Exampl</li> </ul> | es of explicit addr                                                         | esses:                                                          |                                         |    |

|                            | 8 IC 0,11                                                                   | $28(10,7)$ $D_2=1128$ $28(0,7)$ $D_2=1128$ $28(7,0)$ $D_2=1128$ | 3, X <sub>2</sub> =0, B <sub>2</sub> =7 |    |

| Genera                     | I forms of RX-inst                                                          | ruction second op                                               | erands:                                 |    |

|                            |                                                                             | Explicit Address                                                | Implied Address                         |    |

|                            | Not Indexed                                                                 | D <sub>2</sub> (,B <sub>2</sub> )                               | S <sub>2</sub>                          |    |

|                            | Indexed                                                                     | $D_2(X_2, B_2)$                                                 | S <sub>2</sub> (X <sub>2</sub> )        |    |

| Chap. III, Sec. 9          |                                                                             | ystem z Assembler Langua                                        |                                         |    |

|    | Inese             | are s | some typical RS- and SI-t    | ype   | Instru | ctions | 5:                           |

|----|-------------------|-------|------------------------------|-------|--------|--------|------------------------------|

| Ор | Mnem <sup>•</sup> | Гуре  | Instruction                  | Ор    | Mnem   | Туре   | Instruction                  |

| 90 | STM               | RS    | Store Multiple               | 91    | ТМ     | SI     | Test Under Mask              |

| 92 | MVI               | SI    | Move Immediate               | 94    | NI     | SI     | AND Immediate                |

| 95 | CLI               | SI    | Compare Logical<br>Immediate | 96    | 01     | SI     | OR Immediate                 |

| 97 | XI                | SI    | Exclusive OR Immediate       | 98    | LM     | RS     | Load Multiple                |

| 88 | SRL               | RS    | Shift Right Single Logical   | 89    | SLL    | RS     | Shift Left Single<br>Logical |

| 8A | SRA               | RS    | Shift Right Single           | 8B    | SLA    | RS     | Shift Left Single            |

| 8C | SRDL              | RS    | Shift Right Double Logical   | 8D    | SLDL   | RS     | Shift Left Double<br>Logical |

| 8E | SRDA              | RS    | Shift Right Double           | 8F    | SLDA   | RS     | Shift Left Double            |

| _  | Manu              |       | to write their energed fir   | اطما  |        |        |                              |

| •  | Many              | ways  | to write their operand fie   | elds! |        |        |                              |

| _ | riting RS | 71                                   |                                                  |                            | -                                                                                                                                               |   |

|---|-----------|--------------------------------------|--------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | RS-type   | instru                               | uctions h                                        | nave tv                    | wo operand forms:                                                                                                                               |   |

|   | - "RS-1"  | form,                                | , one reg                                        | ister: F                   | $R_1, D_2(B_2)$ or $R_1, S_2$                                                                                                                   |   |

|   | - "RS-2"  | form                                 | , two regi                                       | sters:                     | $R_1, R_3, D_2(B_2)$ or $R_1, R_3, S_2$                                                                                                         |   |

| • | Assembl   | er mu                                | ust gene                                         | rate m                     | nachine language form of the instruction:                                                                                                       |   |

| ſ | opcode    | R1                                   | R3                                               | B2                         | D2                                                                                                                                              |   |

| , | R, opera  | nd de                                | esignate                                         | s a ge                     | neral register; R3 operand can sometime                                                                                                         | s |

| • | be omitte | ed; D                                | <sub>2</sub> (B <sub>2</sub> ) ope               | erand o                    | can be a memory reference or a number                                                                                                           | s |

| • | - ·       | ed; D<br>s of F<br>SRA<br>SLDL<br>LM | 2(B2) ope<br>RS-type<br>11,2<br>6,N<br>14,12,12( | erand o<br>instruc<br>(13) | can be a memory reference or a number                                                                                                           | s |

| • | be omitte | ed; D<br>s of F<br>SRA<br>SLDL<br>LM | 2(B2) ope<br>RS-type<br>11,2<br>6,N<br>14,12,12( | erand o<br>instruc<br>(13) | can be a memory reference or a number<br>ctions:<br>Explicit address (RS-1 form)<br>Implied address (RS-1 form)<br>Explicit address (RS-2 form) | s |

|     | ting SI-Ty                              | •                        |                         | guage form of the                        | 3<br>instruction: |

|-----|-----------------------------------------|--------------------------|-------------------------|------------------------------------------|-------------------|

| r   | DPCODE I                                | TT-                      | D <sub>2</sub>          | 33- · · · · · · · · · · · · · · · · ·    |                   |

| • C | D <sub>1</sub> (B <sub>1</sub> ) (first | ) operand                | designates an ad        | dress-specification                      |                   |

| s s | Second $(I_2)$                          | operand i                | s an <i>immediate</i> o | perand                                   |                   |

| • @ | General for                             | ms of SI-i               | nstruction operan       | ds:                                      |                   |

|     |                                         |                          | Explicit Address        | Implied Address                          |                   |

|     |                                         | SI                       | $D_1(B_1),I_2$          | S <sub>1</sub> ,I <sub>2</sub>           |                   |

| • E | Examples o                              | of SI-type               | instructions            |                                          |                   |

|     | MVI                                     | [ 0(6),C'*<br>[ Buffer,C |                         | D <sub>1</sub> (B <sub>1</sub> ) address |                   |

|     | 02.                                     |                          |                         | 1                                        |                   |

|     |                                         |                          |                         |                                          |                   |

|     |                                         |                          | System z Assembler      |                                          |                   |

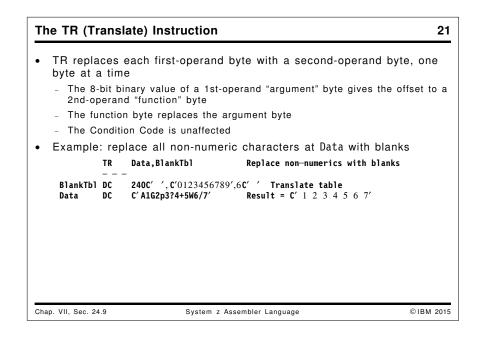

| D5     CLC     1     Compare Logical     D6     OC     1     OR       D7     XC     1     Exclusive OR     DC     TR     1     Translate |    |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| D5     CLC     1     Compare Logical     D6     OC     1     OR       D7     XC     1     Exclusive OR     DC     TR     1     Translate |    |

| D7 XC 1 Exclusive OR DC TR 1 Translate                                                                                                   |    |

|                                                                                                                                          |    |

| E0 SBP 2 Shift And Bound E1 MVO 2 Move With Offs                                                                                         |    |

|                                                                                                                                          | et |

| F2 PACK 2 Pack F3 UNPK 2 Unpack                                                                                                          |    |

| F8 ZAP 2 Zero And Add F9 CP 2 Compare                                                                                                    |    |

| FA AP 2 Add FB SP 2 Subtract                                                                                                             |    |

| FC MP 2 Multiply FD DP 2 Divide                                                                                                          |    |

| The    | Assemt          | oler gene                     | erate          | s two fo          | orms                            | of SS-t                        | ype machi                                      | ne instruc           | ction:           |

|--------|-----------------|-------------------------------|----------------|-------------------|---------------------------------|--------------------------------|------------------------------------------------|----------------------|------------------|

| OPCODE | L               | 1 <sup>B</sup> 1              |                | D <sub>1</sub>    | B <sub>2</sub>                  | D <sub>2</sub>                 | ONE LE                                         | NGTH FIELD ("S       | S-1")            |

| OPCODE | L <sub>1</sub>  | L <sub>2</sub> B <sub>1</sub> |                | D1                | B2                              | D <sub>2</sub>                 | TWO LE                                         | NGTH FIELDS ("       | SS-2")           |

| • Addr | esses a         | a <i>nd</i> leng              | ths c          | an both           | ı be s                          | specifie                       | d explicitly                                   | or implic            | citly.           |

|        | S               | S-1 Form                      |                | Explici           | it Add                          | resses                         | Implied Ad                                     | Idresses             |                  |

|        | Exp             | licit Leng                    | th             | D <sub>1</sub> (N | 1,B1),D                         | <sub>2</sub> (B <sub>2</sub> ) | S <sub>1</sub> (N <sub>1</sub>                 | ),S <sub>2</sub>     |                  |

|        | Imp             | lied Leng                     | th             | D <sub>1</sub> (, | B <sub>1</sub> ),D <sub>2</sub> | (B <sub>2</sub> )              | S <sub>1</sub> ,5                              | S <sub>2</sub>       |                  |

|        |                 | ples of S                     | SS-1           | form in           | struct                          | ions:                          | subtracts o<br>h and address                   |                      | n L <sub>1</sub> |

|        | CLC<br>TR<br>XC | Name (24                      | ),Rec<br>15),7 | Name E<br>(12) 1  | Explici<br>Implied              | it lengtl<br>1 length          | h, implied ac<br>, explicit ac<br>and addresse | ldresses<br>Idresses |                  |

| or i | mplied addresses             | ions, either or both op<br>or lengths<br>e of the possible operand |                                            | plicit |

|------|------------------------------|--------------------------------------------------------------------|--------------------------------------------|--------|

|      | SS-2 Form                    | Explicit Addresses                                                 | Implied Addresses                          |        |

|      | Explicit Lengths             | $D_1(N_1,B_1),D_2(N_2,B_2)$                                        | $S_1(N_1), S_2(N_2)$                       |        |

|      | Implied Lengths              | $D_1(,B_1),D_2(,B_2)$                                              | S <sub>1</sub> ,S <sub>2</sub>             |        |

|      | ZAP Sum(14),0<br>AP Total(15 | ) Num(12) Implied lengt                                            | s explicit addresses                       |        |

|      |                              |                                                                    | ns, explicit addresses<br>ns and addresses |        |

|              | i be io                                       | aded                                 | into me                                         | emory at address X'5000'                                                                                                                                                                     |

|--------------|-----------------------------------------------|--------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5000         |                                               | START                                | X'5000'                                         | STARTING LOCATION                                                                                                                                                                            |

| 5000         |                                               | BASR                                 | 6,0                                             | ESTABLISH BASE ADDRESS                                                                                                                                                                       |

| 5002<br>5006 | BEGIN                                         | A                                    |                                                 | LOAD CONTENTS OF N INTO GR2<br>ADD CONTENTS OF ONE                                                                                                                                           |

| 5000<br>500A |                                               | ST                                   | 2,0NE<br>2.N                                    | STORE CONTENTS OF GR2 INTO N                                                                                                                                                                 |

| 3004         | TWEN                                          |                                      |                                                 | ITIONAL BYTES OF INSTRUCTIONS, DATA, ETC                                                                                                                                                     |

| 5024         | N                                             | DC                                   | F'8'                                            | DEFINE CONSTANT WORD INTEGER 8                                                                                                                                                               |

| 5028         | ONE                                           | DC                                   | F'1'                                            | DEFINE CONSTANT WORD INTEGER 1                                                                                                                                                               |

| -            | The ler                                       | igth of                              | f each st                                       | tatement is added to its starting location (on the left)                                                                                                                                     |

| At           | <i>execu</i><br>Since t                       | <i>tion</i> t<br>he L i              | ime, aft<br>nstructio                           | tatement is added to its starting location (on the left)<br>ter the BASR is executed, $c(R6)=X'00005002'$<br>on wants to refer to the word at X'5024', its displacement<br>4'-X'5002'=X'022' |

| At<br>-      | <i>execu</i><br>Since t<br>from X'<br>So if w | tion t<br>he L i<br>5002 i<br>e crea | ime, aff<br>nstructio<br>is X'5024<br>ate an ac | ter the BASR is executed, $c(R6)=X'00005002'$<br>on wants to refer to the word at X'5024', its displacement                                                                                  |

| Compu                        | uting Displace                                   | ements (continued)                                                                                                                               | 38            |

|------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| • Sup                        | pose this fragn                                  | nent is to be loaded into memory at ad                                                                                                           | dress X'84E8' |